# Clock Buffers: Key parameters and Specifications

**Prepared by Badarish Colathur Arvind**

**Presented by Liam Keese**

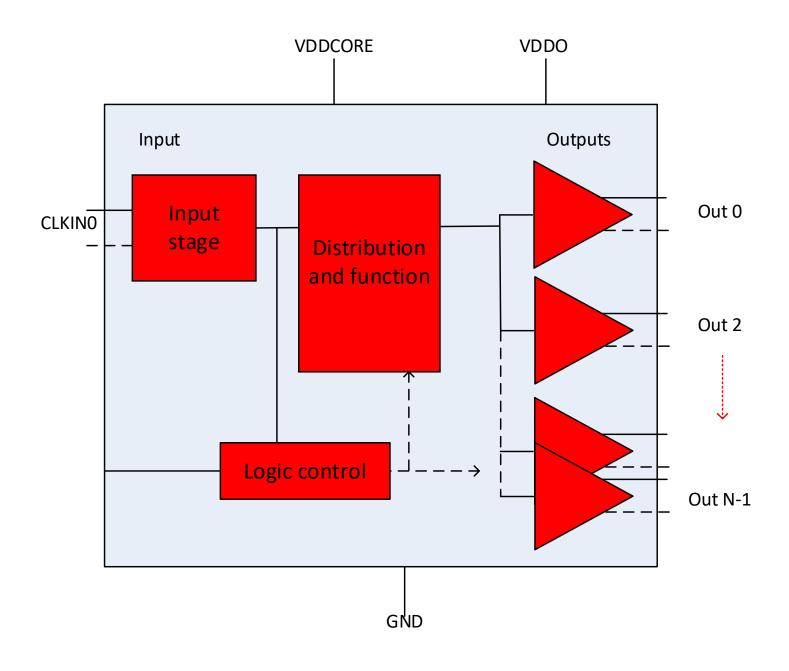

### **Clock buffer overview**

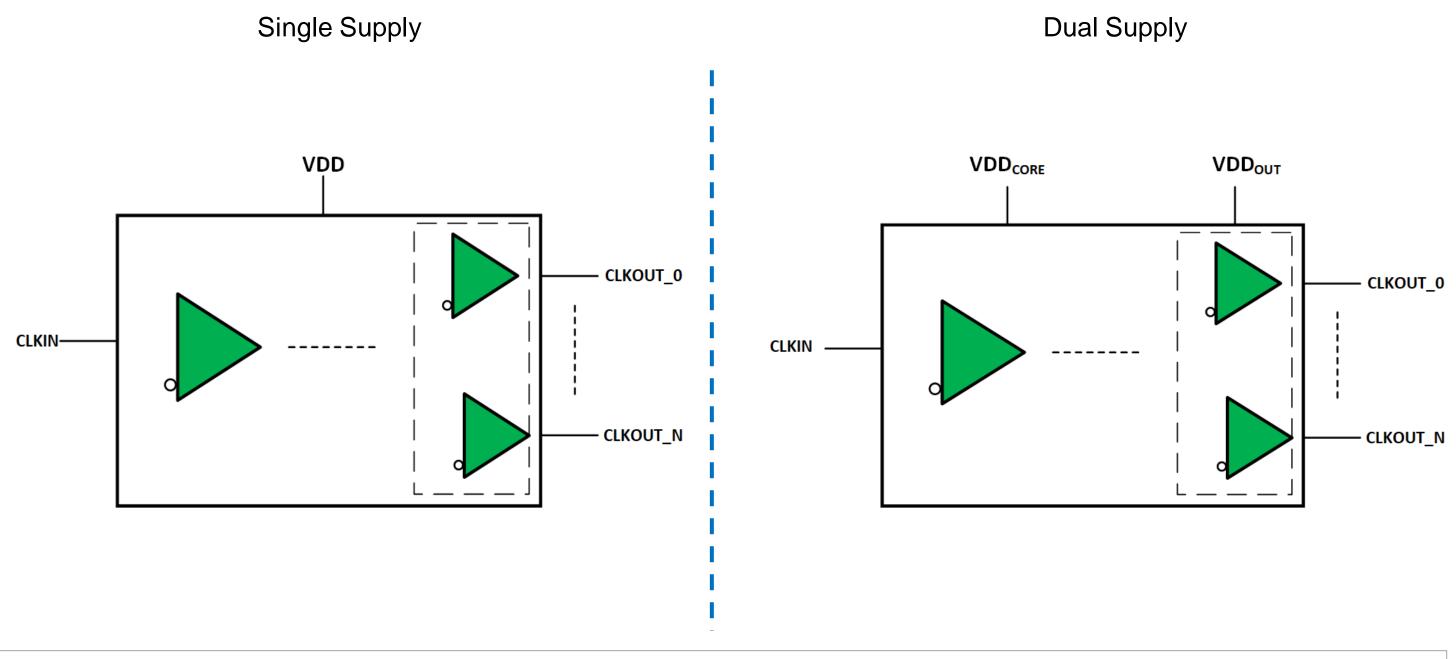

## **Clock buffer voltage supply**

## **Clock buffer input/output format**

|                | Single-ended            | Differential                               |

|----------------|-------------------------|--------------------------------------------|

| Signal format  | CMOS, LVTTL, Sine       | LVDS, LVPECL, HCSL, CM                     |

| Routing        | Simple                  | differential traces need to b              |

| Components     | Fewer                   | ~2x single-ended                           |

| Noise coupling | Prone to noise-coupling | Provides common mode no rejection/coupling |

### ML

#### be matched

#### oise

## **Clock buffer input configuration**

#### Single-ended

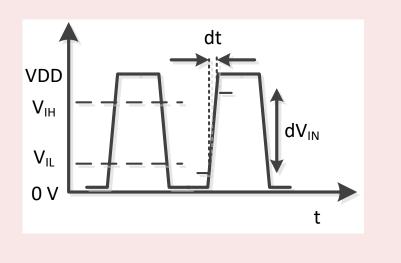

A typical single ended specification looks like the one shown below from <u>LMK1C1104</u>:

| CLOCK IN             | CLOCK INPUT           |                            |                       |                     |      |  |  |

|----------------------|-----------------------|----------------------------|-----------------------|---------------------|------|--|--|

| f <sub>IN_SE</sub>   | Input frequency       | V <sub>DD</sub> = 3.3 V    | DC                    | 250                 | MHz  |  |  |

|                      |                       | $V_{DD}$ = 2.5 V and 1.8 V | DC                    | 200                 |      |  |  |

| VIH                  | Input high voltage    |                            | 0.7 x V <sub>DD</sub> |                     | V    |  |  |

| VIL                  | Input low voltage     |                            |                       | $0.3 \times V_{DD}$ | V    |  |  |

| dV <sub>IN</sub> /dt | Input slew rate       | 20% - 80% of input swing   | 0.1                   |                     | V/ns |  |  |

| I <sub>IN_LEAK</sub> | Input leakage current |                            | -50                   | 50                  | uA   |  |  |

| C <sub>IN_SE</sub>   | Input capacitance     | at 25°C                    |                       | 7                   | pF   |  |  |

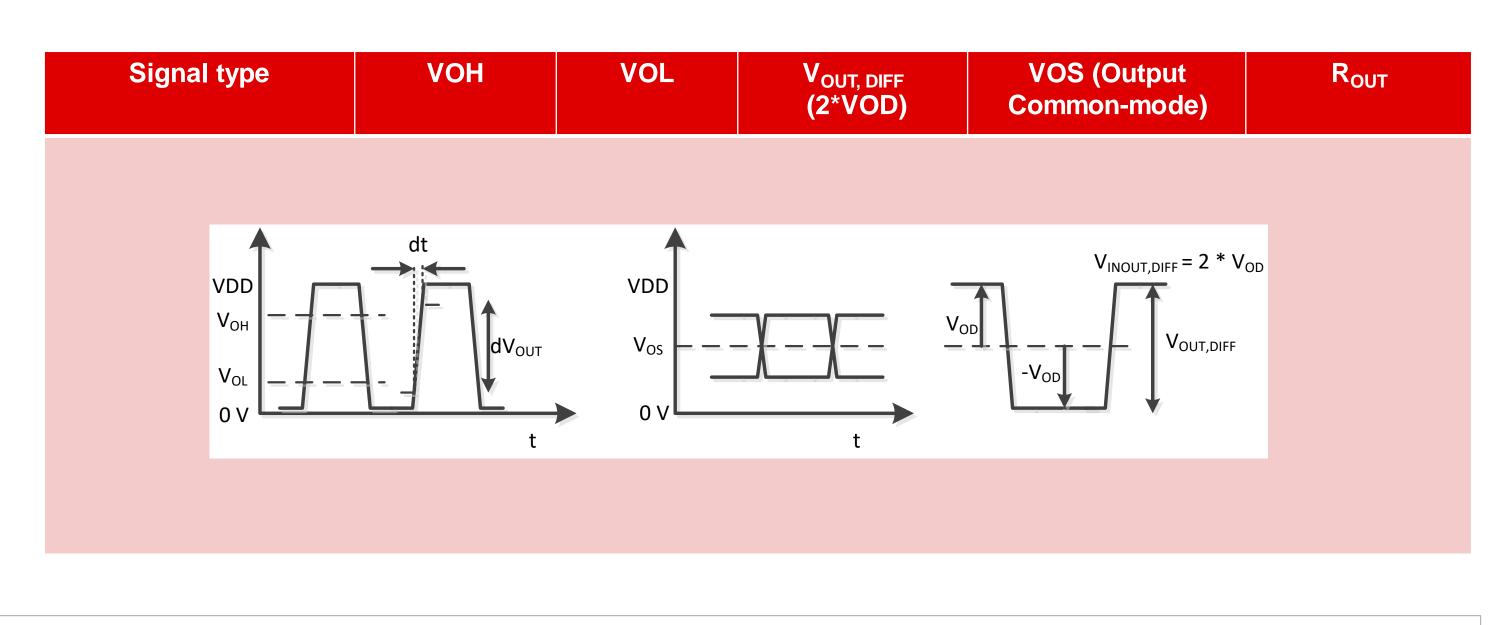

## **Clock buffer output level specifications**

## **Clock buffer output level specifications**

| Signal type          | VOH     | VOL         | V <sub>OUTDIFFP-P</sub><br>(2*VOD) | VOS (Output<br>Common-mode) | R <sub>OUT</sub>                   |

|----------------------|---------|-------------|------------------------------------|-----------------------------|------------------------------------|

| Single-ended: CMOS   | 0.7*VDD | 0.3*VDD     | VDD                                | 0.5*VDD                     | 50 Ω (But not all devices have it) |

| Differential: LVDS   | 1.365 V | 1.015 V     | 700 mV                             | 1.2 V                       | High impedance                     |

| Differential: LVPECL | VDD-1 V | VDD – 1.8 V | 1.6 V                              | VDD – 1.4 V                 | Low impedance                      |

| Differential: HCSL   | 700 mV  | 0 V         | 1.4 V                              | 350 mV                      | High impedance                     |

| Differential: CML    | VDD     | VDD-0.4 V   | 800 mV                             | VDD-0.2 V                   | 50 Ω                               |

## **Clock buffer jitter and phase noise**

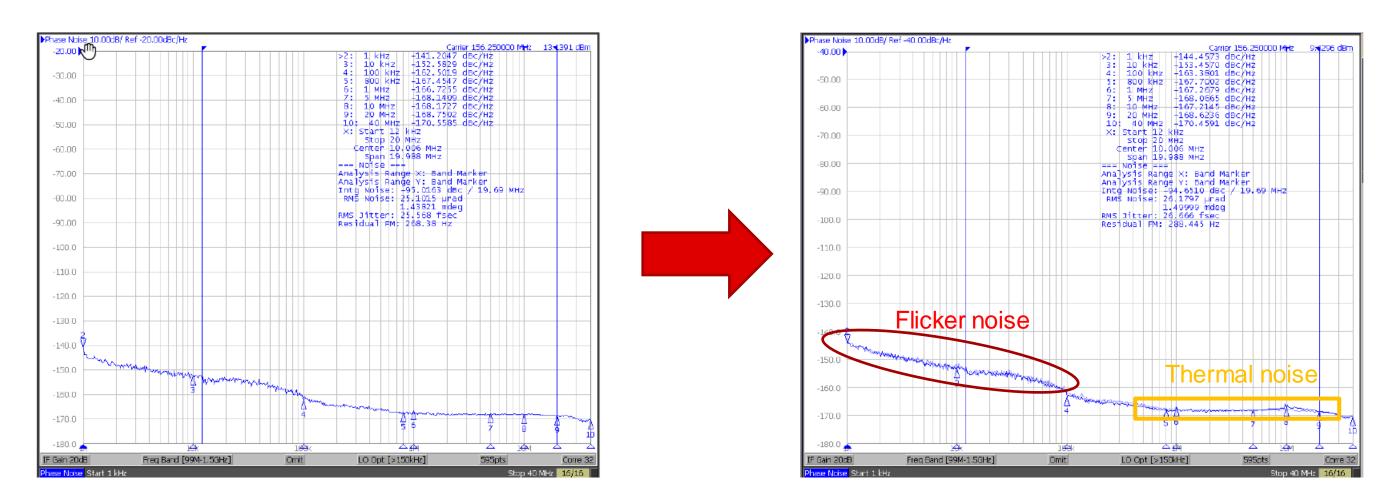

Input clock phase noise @156.25 MHz

Output clock phase noise. The jitter added by the buffer is due to its flicker noise and thermal noise components.

## **Clock buffer jitter and phase noise**

|        | Output<br>Peak to<br>Peak Swing | Input Slew<br>rate | Additive<br>jitter/Phase<br>noise | Summary                                                    |

|--------|---------------------------------|--------------------|-----------------------------------|------------------------------------------------------------|

| CMOS   | VDD                             | High               | 1 <sup>st</sup> (Best)            | Best noise performance due t peak swing.                   |

| LVPECL | 1.6 V                           | High               | 2 <sup>nd</sup>                   | Noise performance is very go swing.                        |

| HCSL   | 1.4 V                           | High               | 3 <sup>rd</sup>                   | Noise performance not as good due to slightly lower swing. |

| LVDS   | 700 mV                          | Low                | 4 <sup>th</sup>                   | Noise performance limited du and slew rate.                |

#### to high peak to

#### ood due to high

#### ood as LVPECL

#### ue to low swing

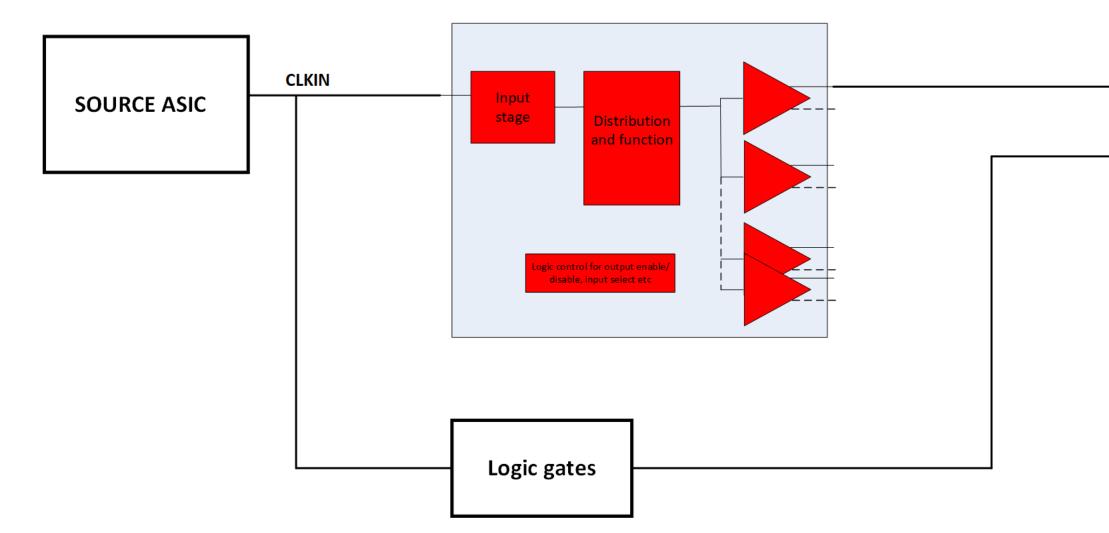

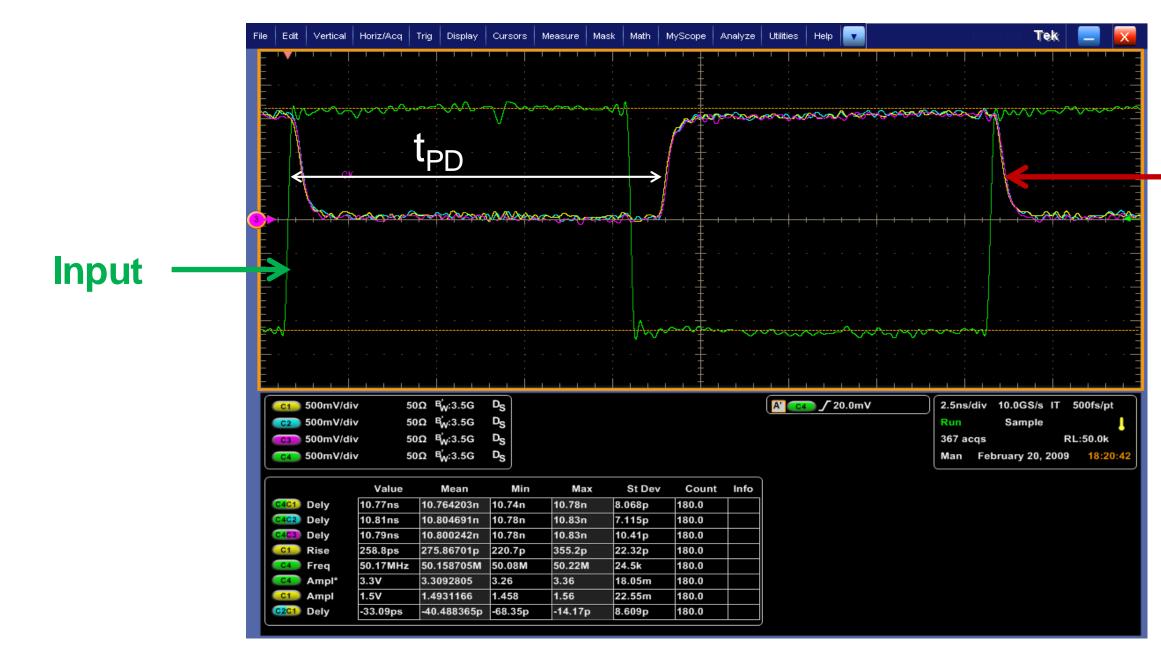

## **Clock buffer propagation delay**

- The various stages of a buffer contribute to propagation delay (t<sub>PD</sub>)

- The input stage and output stage contribute less than the middle stage.

#### **RECEIVE ASIC**

## **Clock buffer propagation delay**

### **Outputs**

### **Clock buffer channel-channel skew**

## **Clock buffer part to part skew**

#### TRANSDUCER

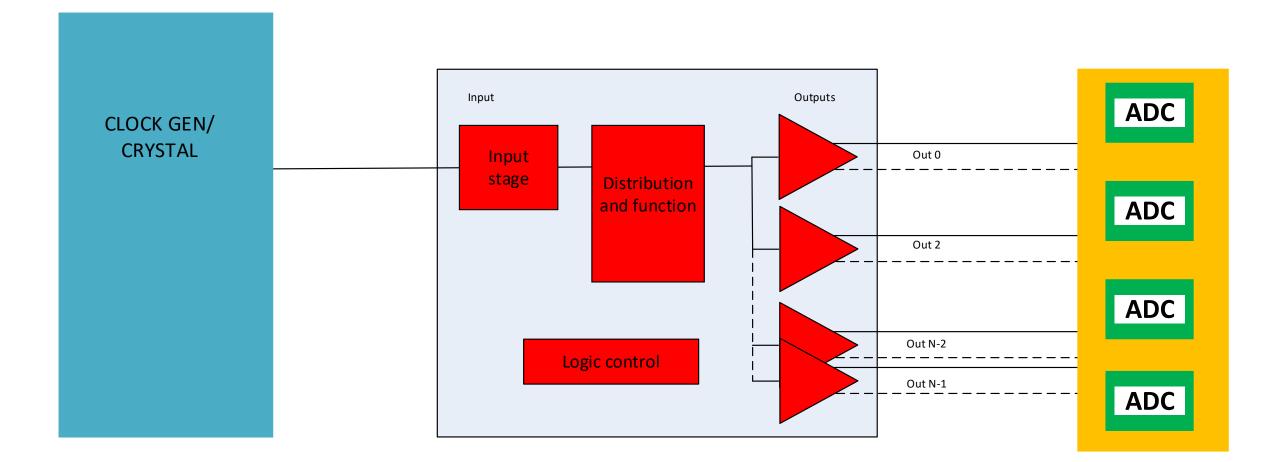

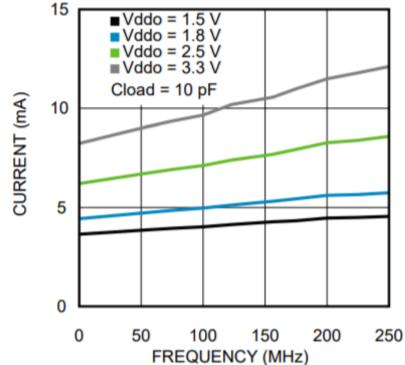

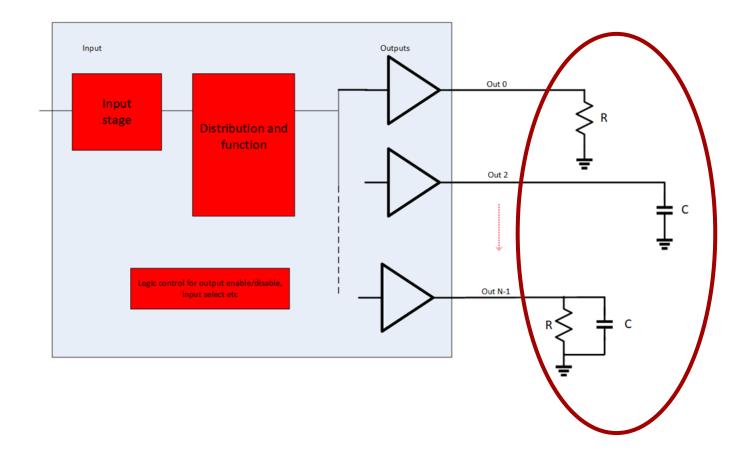

## **Clock buffer power consumption and loading**

Current consumption vs. frequency, Cload = 10pF

## To find more technical resources and search products, visit ti.com/clocks

### ©2020 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty. Use of this material is subject to TI's Terms of Use, viewable at TI.com

## Clock Buffers: Key Parameters and Specifications

### **TI Precision Labs – Clocks and Timing**

**Prepared by Badarish Colathur Arvind**

### Quiz

- True or false: Single ended buffers are immune to external noise coupling

- True or false: For a given VDD, CMOS buffers provide the highest output amplitude

- True or false: Increasing the input slew rate and input amplitude reduces the output additive jitter of the buffer

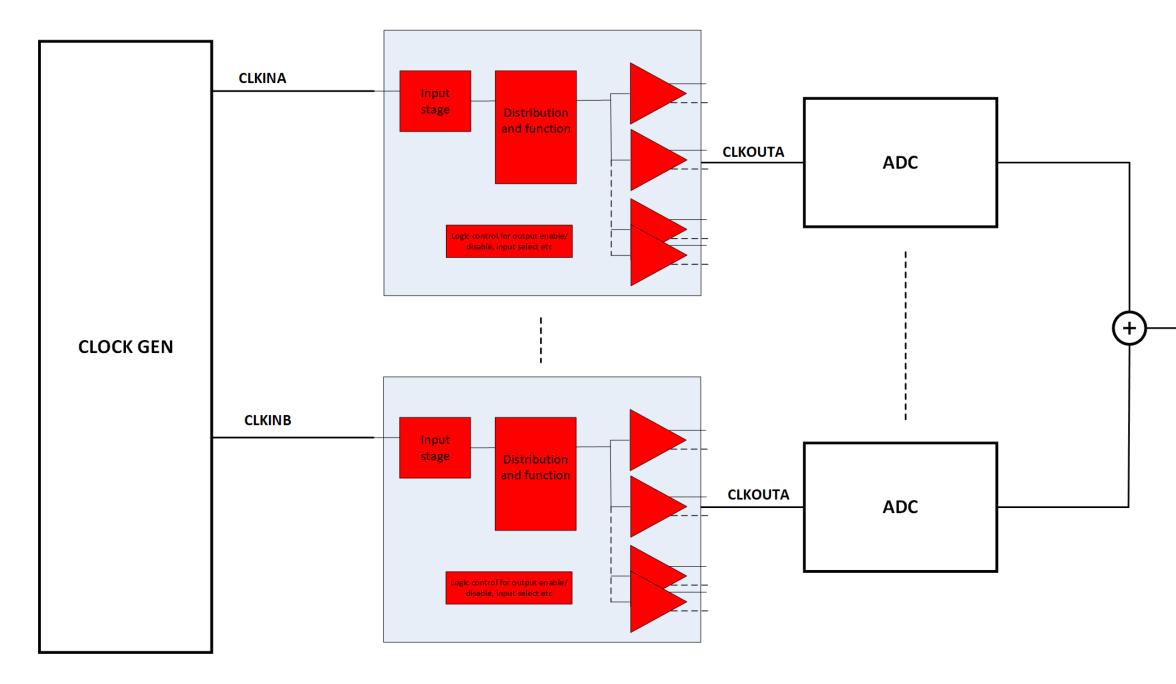

- True or false: An university student connects 4 ADCs in parallel to increase the resolution of her EE101 lab measurement. She uses a 1:4 clock buffer to distribute the clock to the 4 ADCs. The ADC has a specification for device to device aperture delay variation of  $\pm 0.1$  ns, while the buffer has a channel to channel skew of 250 ps. Does the skew specification of the buffer meet the ADC aperture delay requirements

### Quiz

- True or false: Single ended buffers are immune to external noise coupling

- True or false: For a given VDD and a capacitive load, CMOS buffers provide the highest output amplitude

- <u>True</u> or false: Increasing the input slew rate and input amplitude reduces the output additive jitter of the buffer

- True or <u>false</u>: An university student connects 4 ADCs in parallel to increase the resolution of her EE101 lab measurement. She uses a 1:4 clock buffer to distribute the clock to the 4 ADCs. The ADC has a specification for device to device aperture delay variation of  $\pm 0.1$  ns, while the buffer has a channel to channel skew of 250 ps. Does the skew specification of the buffer meet the ADC aperture delay requirements

### **TEXAS INSTRUMENTS**

3

## To find more technical resources and search products, visit ti.com/clocks