# **Frequency Planning Part 2** TI Precision Labs – Clocks and Timing

Presented by Rob Rodrigues

**Prepared by Hao Zheng**

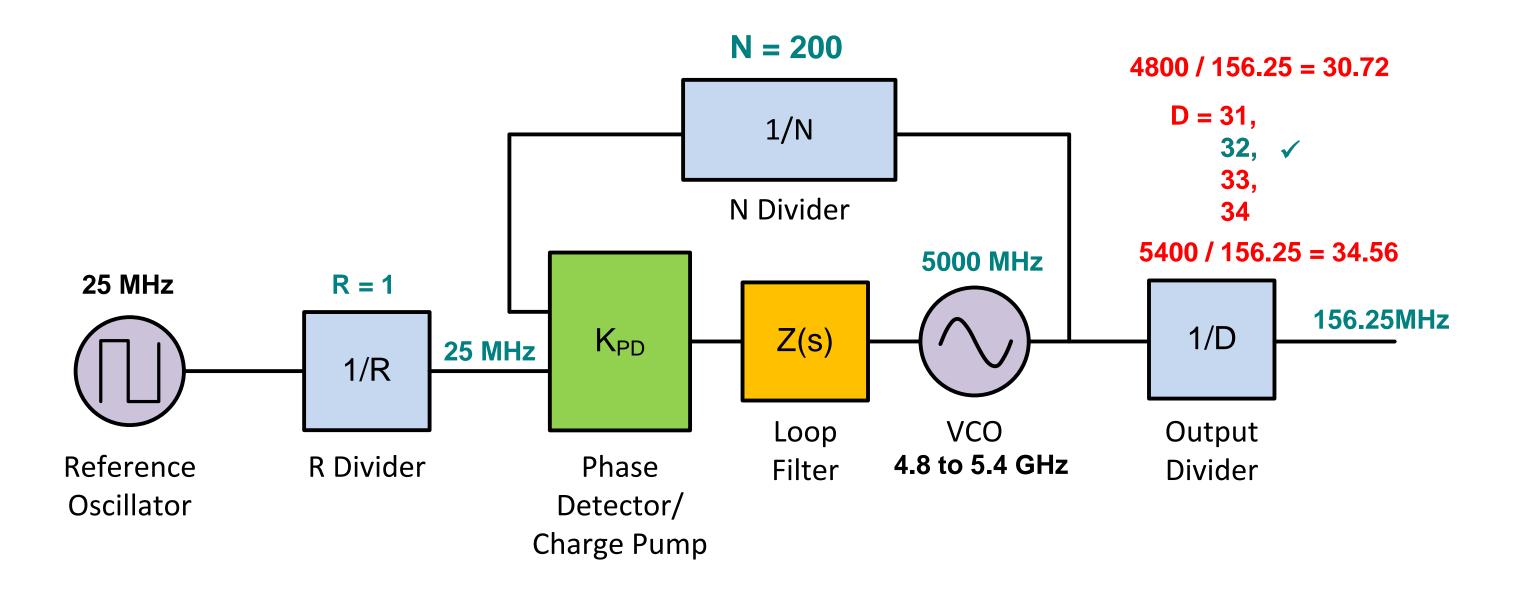

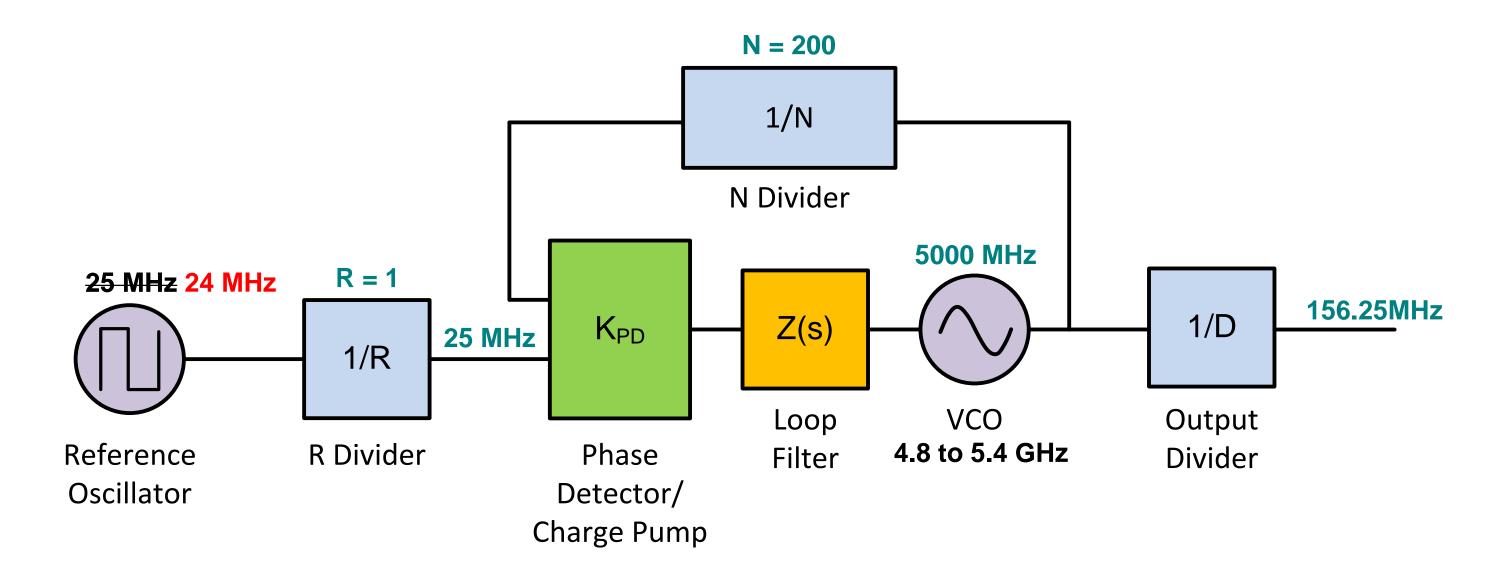

# **Frequency calculation quick review**

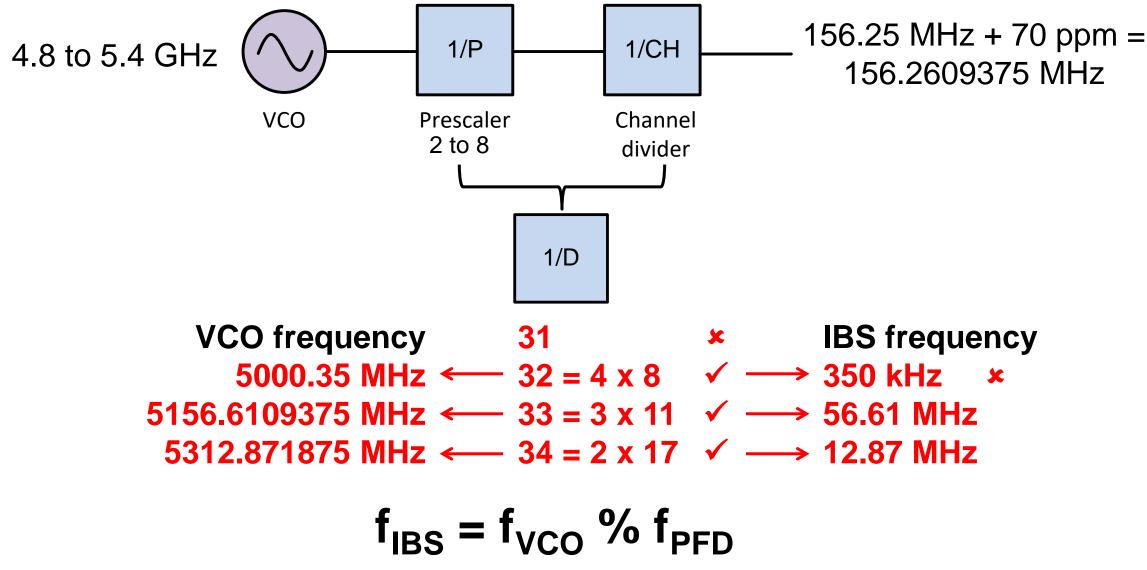

# VCO selection and spur mitigation

How to generate 156.25 MHz + 70 ppm from 100 MHz PFD frequency?

# Mitigate spurs (cont.)

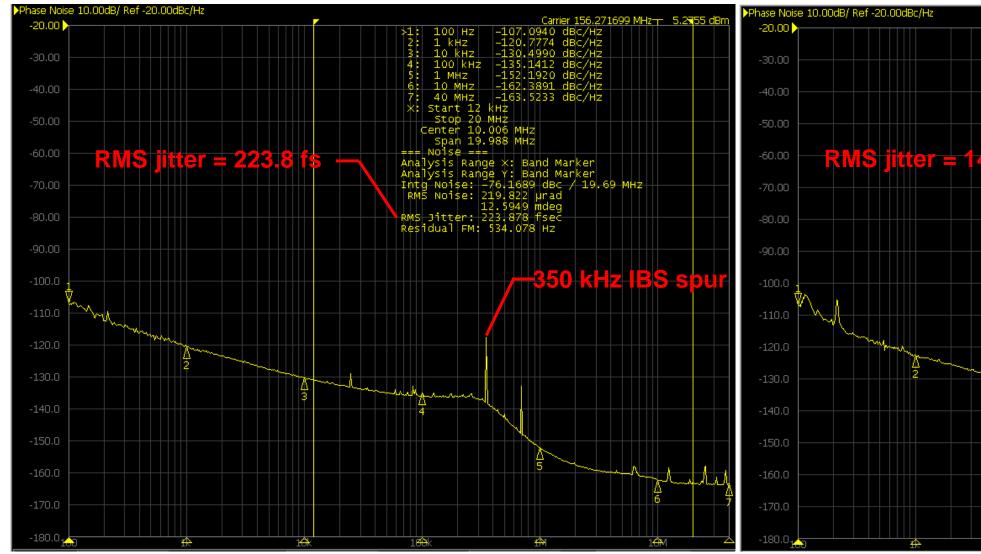

### D = 32

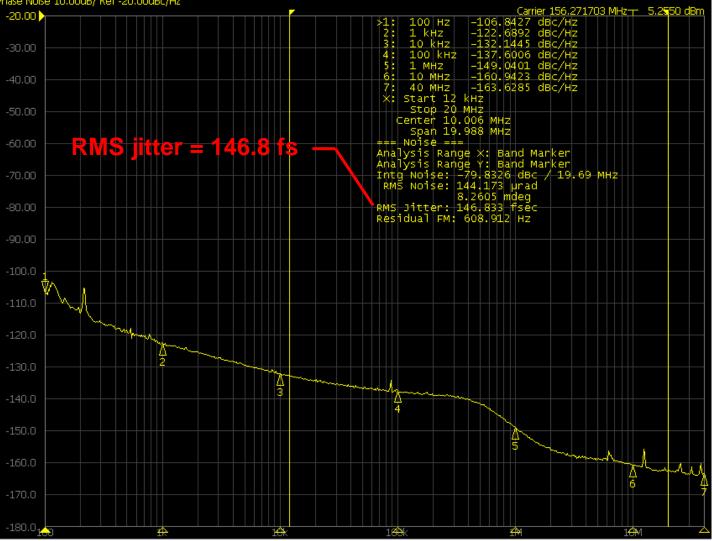

## D = 33

4

# **Frequency calculation and PFD frequency**

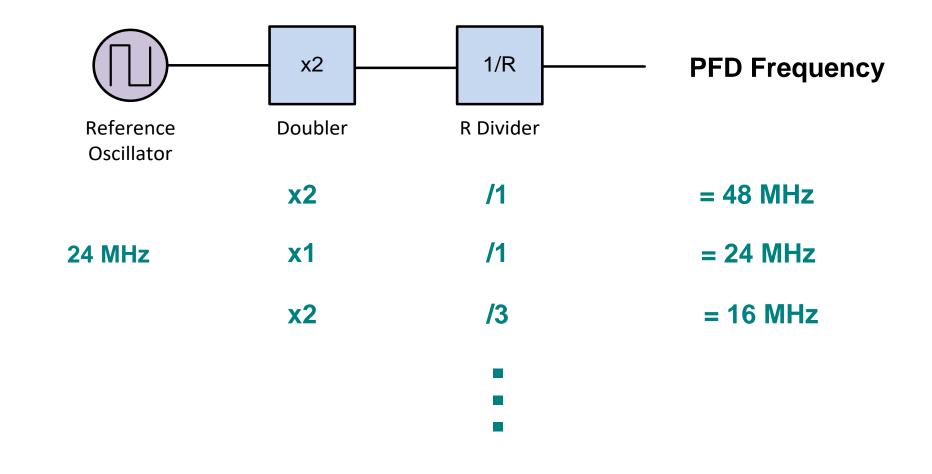

# **Setting PFD frequency**

## **Crosstalk considerations**

# To find more clocks and timing technical resources and search products, visit ti.com/clocks

© Copyright 2019 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's Terms of Use, viewable at TI.com

The Integer Boundary Spur should be as close to the carrier frequency as possible.

The Integer Boundary Spur should be as close to the carrier frequency as possible.

The PFD frequency should be as low as possible for the PLL to always work in integer mode.

The PFD frequency should be as low as possible for the PLL to work in integer mode.

Channel crosstalk is intrinsic and cannot be improved or worsened by board design.

Channel crosstalk is intrinsic and cannot be improved or worsened by board design.