# TI TECH DAYS

# Getting started with the new PSpice<sup>®</sup> for TI design and simulation tool

Ian Williams

APP – LP – LDO

#### About me – Ian Williams Business lead, Low-Voltage LDOs

- Career

- **UT DALLAS** - BSEE University of Texas at Dallas, 2009

- TI since 2009, LDO since July 2020

- Expertise

- 11 years working with various types of amplifiers

- Co-creator of GWL amplifier SPICE model architecture

- Co-creator of TI Precision Labs Op Amps

- Fun fact

- Big music guy have performed at festivals, DJ'd at clubs and on FM radio, and even met my wife at Coachella 2013

### Agenda

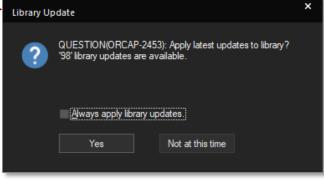

- TI simulation tools overview 10 min.

- PSpice<sup>®</sup> for TI deep dive 10 min.

- Features and limitations

- Built-in model library

- Setup and simulation examples 25 min.

- Operational amplifier: OPA211

- Power supply: TPS7A52

- Modeling Application: Power MOSFET

- Additional resources

Please ask your questions in the chat!

# Part 1 TI simulation tools overview

**Tip:** SPICE stands for "Simulation Program with Integrated Circuit Emphasis"

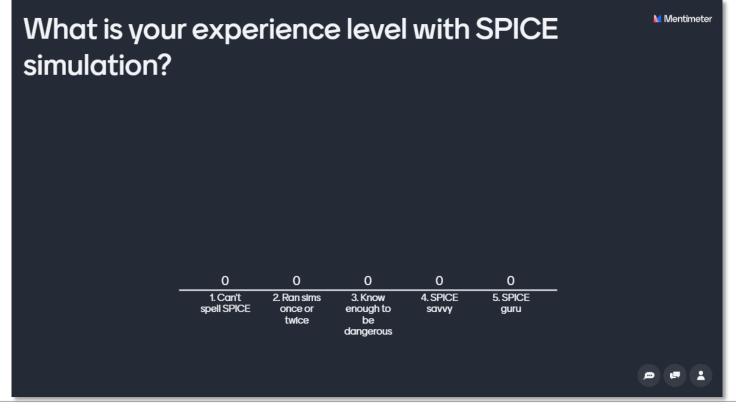

#### Time for some audience participation...

### Introducing PSpice<sup>®</sup> for TI

## PSpice for TI will help engineers speed time to market and reduce development costs, delivering:

- Full-featured simulation of entire systems.

- Advanced capabilities, including Monte Carlo and worst-case analysis.

- Synchronized library of >5,700 models and counting.

- No design size limitations.

- Easy transition to layout and prototype.

- Integrated design resources.

- Quick access to TI product information.

- No need to manually upload new TI models.

## Why is TI partnering with Cadence?

#### **Growing demand**

There is an increased need for simulation software to test new design concepts, accelerate product development and demonstrate regulatory compliance.

Source: ABI Research

#### Short design timelines

Today's design engineers must produce accurate designs on tight deadlines — in many cases, reducing the prototyping and evaluation phases of their designs.

#### Desire for more advanced simulation

Existing simulation tools in the market lack advanced analysis capabilities, model portability and flexibility, and easy library synchronization.

"Tools that are intuitive and include system-level simulation capabilities can cut the development time and speed time to market." – Kevin Anderson, Omdia

### Is PSpice for TI replacing other TI tools?

### **PSpice for TI vs. TINA-TI**

|                                                        | PSpice for TI                            | TINA-TI                   |  |

|--------------------------------------------------------|------------------------------------------|---------------------------|--|

| Analysis / simulation                                  |                                          |                           |  |

| AC, Noise, BIAS point, DC sweep,<br>Transient, Fourier | Yes                                      | Yes                       |  |

| Variable sweeps                                        | Temperature,<br>component,<br>parametric | Temperature,<br>component |  |

| Monte Carlo analysis                                   | Yes                                      | No                        |  |

| Worst case analysis                                    | Yes                                      | No                        |  |

| Libraries / components                                 |                                          |                           |  |

| Internal libraries                                     | ~5700                                    | ~1300                     |  |

| Automatic library updates                              | Yes                                      | No                        |  |

| Built-in modeling application                          | Yes                                      | No                        |  |

| Schematics                                             |                                          |                           |  |

| Create hierarchical schematic                          | Yes                                      | No                        |  |

| Multipage schematics                                   | Yes                                      | No                        |  |

# Part 2 PSpice for TI deep dive

Tip: PSpice for TI runs offline!

#### **Software features and limitations FAQ**

- Q. Does PSpice for TI work offline?

- A. Yes, an internet connection is not required to run.

- Q. Is there a maximum number of nodes?

- A. No, there are no design size limitations. You can also use multi-page schematics and hierarchical blocks.

- **Q.** Are there any other limits to be aware of?

- **A.** Yes. The tool is designed primarily as a SPICE simulation environment for use with the built-in TI models. If third-party models are imported, then only three nodes can be probed simultaneously.

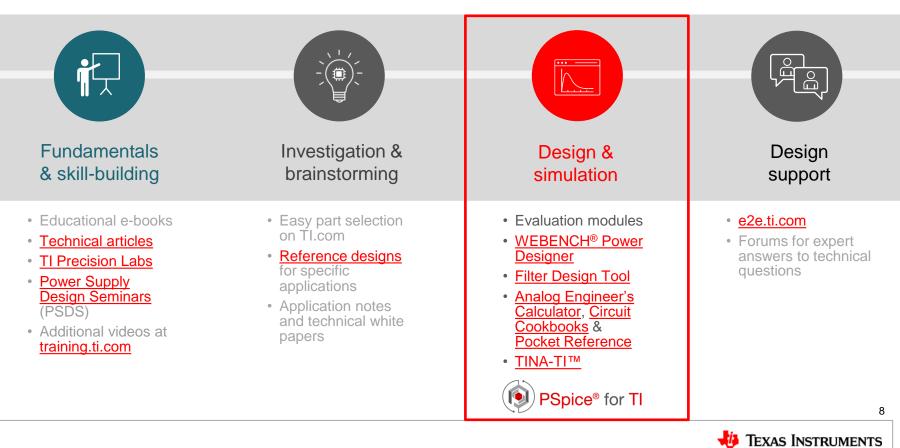

### **Built-in TI model library**

Includes device-specific test benches To accelerate your development

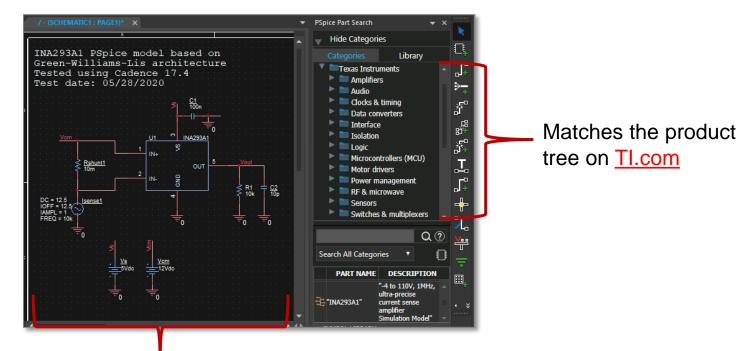

### How do I update the TI model library?

- Updates to the model library are automatically detected and performed at software startup.

- The user can choose not to update.

- The model library is installed locally on the user's hard drive. Models can be copied and imported into other tools if desired.

- Location: C:\SPB\_Data\cdssetup\pspTILibDir

| ← → ► ↑ C:\SPB_Data\cdssetup\pspTiLibDir 		 ♂ |                    |             |      |     |  |  |

|-----------------------------------------------|--------------------|-------------|------|-----|--|--|

| Name ^                                        | Date modified      | Туре        | Size | ^   |  |  |

| download                                      | 11/13/2020 8:18 AM | File folder |      |     |  |  |

| ReferenceDesign                               | 11/12/2020 4:33 PM | File folder |      | l i |  |  |

| 📑 74AC11000.lib                               | 4/3/2020 11:01 PM  | LIB File    | 8 KB |     |  |  |

| 🗋 74AC11000.libsig                            | 7/18/2020 1:06 AM  | LIBSIG File | 1 KB |     |  |  |

| 74AC11000.OLB                                 | 4/3/2020 11:04 PM  | OLB File    | 7 KB |     |  |  |

| 📑 74АС11004.ІіЬ                               | 4/3/2020 11:01 PM  | LIB File    | 7 KB |     |  |  |

| 🗋 74AC11004.libsig                            | 7/18/2020 1:06 AM  | LIBSIG File | 1 KB |     |  |  |

| 24AC11004.OLB                                 | 4/3/2020 11:04 PM  | OLB File    | 7 KB |     |  |  |

#### Are models editable?

- Models are text files and may be edited with a text editor (I recommend <u>Notepad++</u>) from the library directory

- Note: editing TI models breaks their signature, causing the tool to treat them as 3<sup>rd</sup>-party

- Some models have usereditable parameters. Editing these <u>does not</u> break signature.

- If you edit a model and save it in the same location, it will get over-written during the next library update.

| 37 | .SUBCKT 74AC11000 Y A B VCC AGND                                             |

|----|------------------------------------------------------------------------------|

| 38 | XU1 Y A B VCC AGND LOGIC_GATE_2PIN_OD_LVC_2i_NAND_PP_CMOS_74AC11000          |

| 39 | .ENDS                                                                        |

| 40 | .SUBCKT LOGIC_GATE_2PIN_OD_LVC_2i_NAND_PP_CMOS_74AC11000 OUT A B VCC GND     |

| 41 | . PARAM VCC_ABS_MAX = 7                                                      |

| 42 | .PARAM VCC_MAX = 5.5                                                         |

| 43 | . PARAM RA = 220000000                                                       |

| 44 | .PARAM RB = 220000000                                                        |

| 45 | .PARAM CA = 3.5e-12                                                          |

| 46 | .PARAM CB = 3.5e-12                                                          |

| 47 | .PARAM ROEZ = 104.9999999999999                                              |

| 48 | .PARAM COEZ = 3.5e-12                                                        |

| 49 | RA A GND {RA}                                                                |

| 50 | RB B GND {RB}                                                                |

| 51 | CA A GND {CA}                                                                |

| 52 | CB B GND {CB}                                                                |

| 53 | XUA NA A VCC GND LOGIC_INPUT_LVC_2i_NAND_PP_CMOS_74AC11000                   |

| 54 | XUB NB B VCC GND LOGIC_INPUT_LVC_2i_NAND_PP_CMOS_74AC11000                   |

| 55 | XUG NA NB NOUTG VCC GND LOGIC_FUNCTION_2_LVC_2i_NAND_PP_CMOS_74AC11000       |

| 56 | XOUTPD NOUTG NOUTTPD VCC GND TPD_LVC_2i_NAND_PP_CMOS_74AC11000               |

| 57 | XUOUT NOUTTPD NOUT_INT VCC GND LOGIC_PP_OUTPUT_LVC_21_NAND_PP_CMOS_74AC11000 |

| 58 | XICC VCC GND NVIOUT LOGIC_ICC_LVC_2i_NAND_PP_CMOS_74AC11000                  |

| 59 | SICC VCC GND VCC GND SW1                                                     |

Model file example

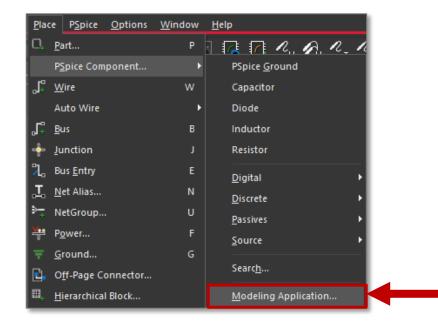

### **Modeling application**

- Used to add customizable, parameterized components to your design:

- Power MOSFETs

- Power diodes

- Passives with parasitics

- Independent sources

- Switches

- Transformers

- Click Place → PSpice Component...

→ Modeling Application in the top menu bar

- Note: these components <u>do not</u> trigger the probe limit

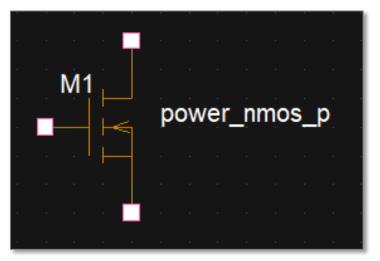

### Modeling application, cont.

- A simple UI opens for each type of component with editable fields

- Customize each parameter to your liking, then click *Place* to drop in schematic

- Note: Device parameters can still be edited from their properties once in the schematic

| N Channel MOSFET                               | P Char | nnel MOSFET | т |

|------------------------------------------------|--------|-------------|---|

| Device Specification                           |        |             |   |

| Parameter                                      | Value  |             |   |

| Reverse transfer capacitance (Crss)            | 58p    | F           |   |

| Input capacitance (Ciss)                       | 1170p  |             |   |

| Output capacitance (Coss)                      | 136p   | F           |   |

| Drain-to-source voltage (BVDss)                | 30.0   |             |   |

| Drain-to-source on-resistance (RdsON)          | 0.0059 | Ohm         |   |

| Series gate resistance (Rg)                    | 1.8    | Ohm         |   |

| Gate-to-source threshold voltage (Vgs_th)      | 1.5    | V           |   |

| Diode forward voltage (VSD)                    | 0.8    |             |   |

| Drain-to-source leakage current (ldss)         |        | Α           |   |

| Total gate charge (QG)                         | 17.2n  |             |   |

| Voltage for specified total gate charge (V_QG) | 10     | С           |   |

| Forward trans-conductance (GFS)                | 44     |             |   |

Power MOSFET window

Power NMOS in schematic

#### **Additional included model libraries**

• These standard PSpice libraries are also included:

| Library  | Description                                                   |  |  |  |

|----------|---------------------------------------------------------------|--|--|--|

| ABM      | Analog behavioral models for various math functions           |  |  |  |

| ANALOG   | Passives, dependent sources, switches, transmission lines     |  |  |  |

| BREAKOUT | Customizable versions of many device types                    |  |  |  |

| DIG_MISC | Digital timing control, pull-up / pull-down resistors         |  |  |  |

| DIG_PRIM | Logic gates, flip-flops                                       |  |  |  |

| SOURCE   | Independent voltage and current sources                       |  |  |  |

| SPECIAL  | Parameters, simulation control, library management, utilities |  |  |  |

Note: components from these libraries <u>do not</u> trigger the probe limit

#### Importing third-party or custom models

- With your *project* (.opj) selected, click *Tools* → *Generate Part*

- Browse to your model file in the new window, make your selections, and click OK

- The new model appears in your project's library

| PSpice for TI-[/ - (SCHEMATIC1 : PAGE1)] | Generate Part ×                                                                              | pspice demo.opj                                                                                                 |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                          | Netlist/source file:                                                                         | Analog or Mixed A/D                                                                                             |

| File Design Edit View Tools Place PSpice | C:\Users\a0282827\Desktop\Custom Model.lib Browse<br>Cancel                                  | File 🖡 Hierarchy                                                                                                |

| 🗋 🗁 💾 📻 🚬 🦉 Annotate                     | Netlist/source file type:<br>PSpice Model Library  +                                         | Design Resources                                                                                                |

| Update Properties                        | Part name: FPGA Setup                                                                        | الله المعالم ال |

| X 🗋 🖬 S ¢   🚊                            | CUSTOM_MODEL                                                                                 | E Library                                                                                                       |

| Test Bench                               |                                                                                              | i د:\users\a0282827\desktop\custom model.olb                                                                    |

| pspice demo.opj                          | Destination part Ibrary:<br>C:\Users\a0282827\Desktop\Custom Model.DLB Browse                |                                                                                                                 |

| Analog or Mixed A/D 🔳 Bill of Materials  | Create new part     O Update pins on existing part in library.                               | Library Cache                                                                                                   |

| File 🙀 Hierarchy Export Properties       | Pick symbols manually                                                                        | Layout                                                                                                          |

|                                          | Sort pins Additional pins Secret in number of additional                                     | Outputs                                                                                                         |

| Design Resources Import Properties       | <u>□ D</u> escending order <u>□</u> pins on part <u>□</u> pins or part <u>□</u> pins or part | PSpice Resources                                                                                                |

| ■ ﷺ .\pspice demo.d                      |                                                                                              |                                                                                                                 |

|                                          | Retain alpha-numeric pin-numbers. Device is pin grid array type package. Indementation       |                                                                                                                 |

| PAGE1 Split Part                         | Implementation type: Implementation name:                                                    |                                                                                                                 |

| 🚊 🛅 Design Cacl 🛛 Customize              | PSpice Model  CUSTOM_MODEL                                                                   |                                                                                                                 |

| E Library                                | Imglementation file:                                                                         |                                                                                                                 |

| taning c:\users\a02 Compare Designs      |                                                                                              |                                                                                                                 |

|                                          |                                                                                              |                                                                                                                 |

**TEXAS INSTRUMENTS**

18

### Types of models on Tl.com

| Туре                 | Description                                                                                                                                                   |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSpice               | Analog / mixed-signal model for use in <b>PSpice-based</b> simulators. Packaged in a way to be easy to import and use in PSpice / Cadence / OrCAD.            |

| TINA-TI              | Analog / mixed-signal model for use in <b>PSpice-based</b> simulators. Packaged in a way to be easy to import and use in TINA-TI.                             |

| HSPICE<br>(uncommon) | Analog / mixed-signal model for use in <b>HSPICE-based</b> simulators. HSPICE is a branch of SPICE similar to PSpice, but models are not directly compatible. |

| SIMPLIS              | Switch-mode power supply model for use in <b>SIMPLIS</b> .                                                                                                    |

| IBIS                 | I/O Buffer Information Specification model, typically used for digital pin timing analysis. Compatible with a broad range of industry simulators.             |

# Part 3 Setup and simulation examples

**Fip:** Enabling AutoConverge in your sim profile can fix a broad range of convergence issues.

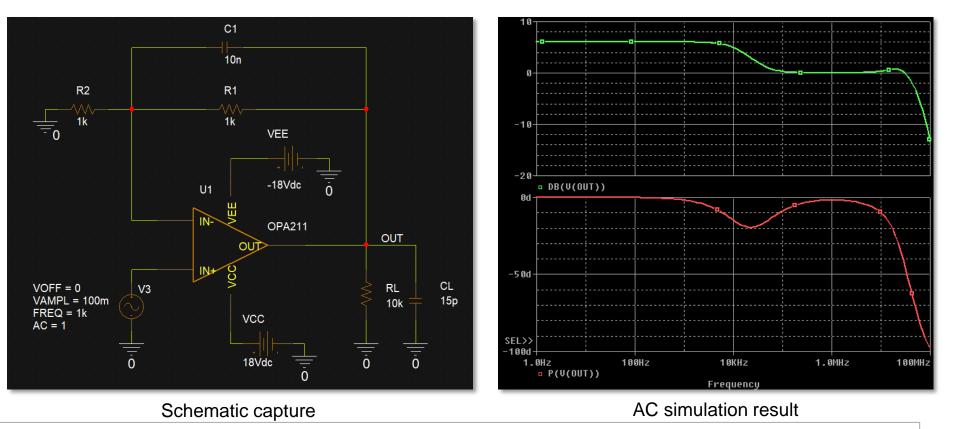

### **Operational amplifier example – OPA211**

21

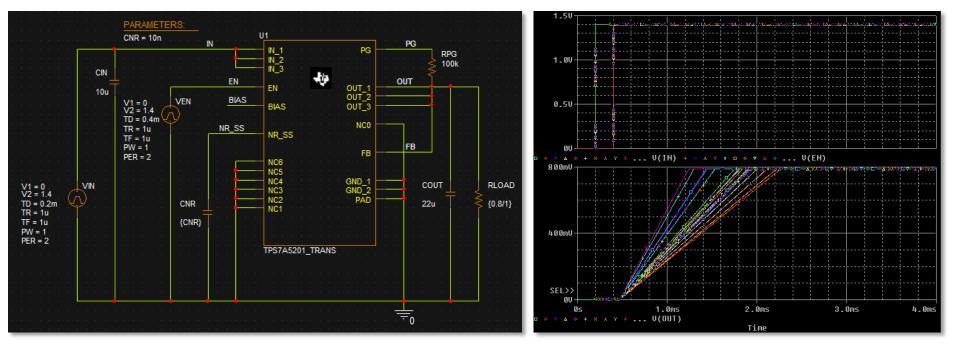

#### **Power supply example – TPS7A52**

Schematic capture

Transient simulation result

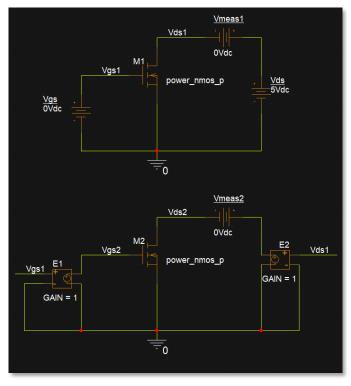

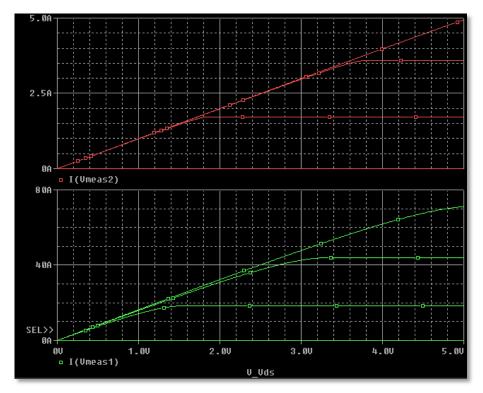

### **Modeling Application – Power MOSFET**

Schematic capture

#### DC simulation result

# Part 4 Additional Resources

Tip: Choose the "Last Plot" setting in your sim profile to preserve results display settings between runs.

### **Additional resources**

#### Hands-on training manual

- Self-guided, step-by-step tutorial that walks the user through the entire tool workflow

- Includes basic and more advanced content

- Includes debugging and troubleshooting

- Available from the PSpice for TI start page:

- Click Training Course

#### cādence°

#### Mixed-Signal Simulation with TI- PSpice 2020® Simulation Labs

This lab manual uses hands-on exercises for both new and moderately experienced users of Cadence® PSpice® to maximize the performance of their circuits.

#### Who will this benefit?

"Engineers and managers dealing with PCB designs, hardware, SPICE models, systems design, FPGA designs, RF circuits, analog/mixed or digital simulations, EMI /EMC analyses, or electronics in general."

#### Quickly Create Schematic for PSpice Simulation

Learn how to quickly design your circuit idea in the OrCAD workspace & get it ready for PSpice simulation to see how it will behave in real world

#### Import 3rd party models in your design

Take advantage of the ability to bring in any third-party vendor model from internet into PSpice

#### Learn Different Types of Analysis Techniques

Learn when to use and how to configure and run the following analyses:

- Transient, AC Sweep, DC Sweep Analysis

Parametric & Performance Analysis

- Parametric & Performance Analysis

Temperature

- Noise

Software Product Version 17.4 - 2019

#### Quickly Solving Convergence errors

Learn how to resolve the most common Spice circuit convergence errors with PSpice and use Auto Convergence to converge a simulation automatically

cādence

1 Page

#### Additional resources, cont.

TI.com/pspice-for-ti

26

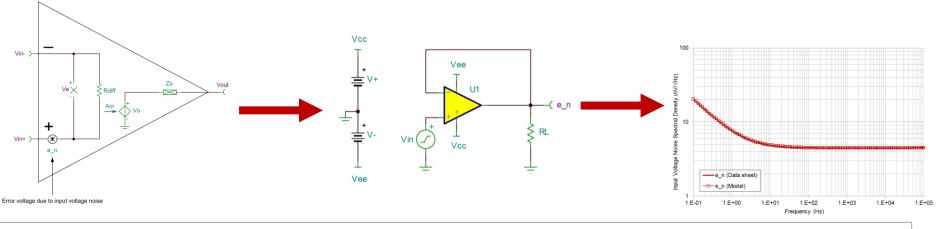

# "Trust, but verify" SPICE models

- Series of articles that covers verifying parameters of amplifier models:

- Part 1: Output impedance

- Part 2: <u>Small-signal bandwidth</u>

- Part 3: <u>Input-referred errors</u>

- Part 4: <u>Noise</u>

### **Direct support from TI**

- For tool-related support: Simulation, hardware & system design tools forum

- For specific model or product support: post to that product's forum

- i.e. For amplifier support, post to the <u>Amplifiers forum</u>

| 🔱 Texas Instruments |                     | Search through millions of questions and answers |               |                 |      |                       | ٩                         |

|---------------------|---------------------|--------------------------------------------------|---------------|-----------------|------|-----------------------|---------------------------|

| E2E™ support foru   | MS Forums           | Technical articles                               | TI training   | Getting started | IMDS | ✓ More                |                           |

| Amplifiers          | Audio               |                                                  | Clock & timir | ng              |      | Data converters       | DLP <sup>®</sup> products |

| Logic               | Microcontrollers    |                                                  | Motor driver  | s               |      | Power management      | Processors                |

| Site support        | Switches & multiple | exers                                            | Tools         |                 |      | Wireless connectivity | Archived forums           |

|                     |                     |                                                  |               |                 | ,    |                       |                           |

**Note:** these forums are all supported by TI applications engineers who are graded on responsiveness and quality of support. You should get an initial reply in 24h.

#### **SPICE** tips – analysis parameters

| Option       | Default | Relaxed | Effect                                                                                             |  |

|--------------|---------|---------|----------------------------------------------------------------------------------------------------|--|

| AutoConverge | Off     | On      | Relaxes multiple parameters if needed to enable convergence                                        |  |

| ABSTOL       | 1e-12   | 1e-10   | Sets the absolute tolerance of<br>nodal currents between DC<br>iterations                          |  |

| RELTOL       | 1e-3    | 3e-3    | Sets the relative tolerance of the<br>nodal voltages at each DC<br>iteration compared to the first |  |

| GMIN         | 1e-12   | 1e-10   | Adds conductance parallel to every p-n junction                                                    |  |

| CSHUNT       | 0       | 1e-15   | Adds capacitance from every node to ground                                                         |  |

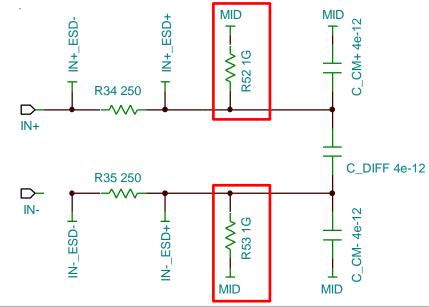

### **SPICE tips – DC path to GND**

- Ensure DC path to ground at every node

- Can force a path with large resistors (1T, etc.) that don't affect electrical performance

- Try to use the smallest value possible

#### **SPICE tips – linear circuits**

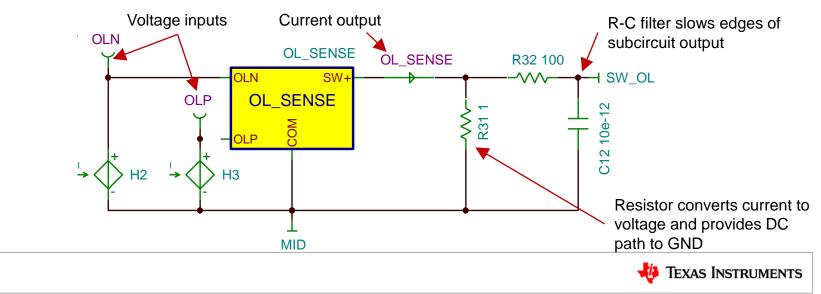

- Design functional blocks with as linear behavior as possible

- Sharp transitions or discontinuities cause issues with convergence checks

- Use R-C filter networks to reduce bandwidth of subcircuits for smooth transitions

- Use voltage inputs and current outputs wherever possible

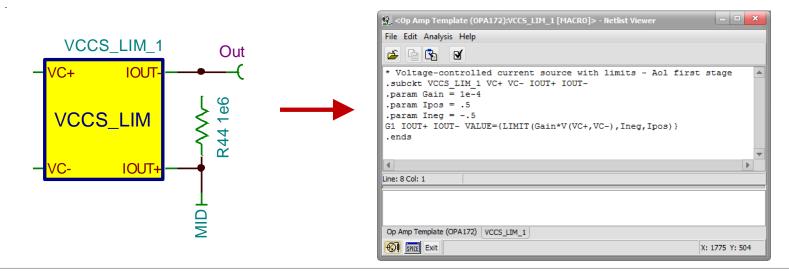

#### **SPICE tips – bounded matrix**

- Keep matrix equations as tightly bounded as possible

- Place limits on gain and buffer stages

- Use only as much gain as required

- Scale resistances to keep node voltages and currents in similar ranges

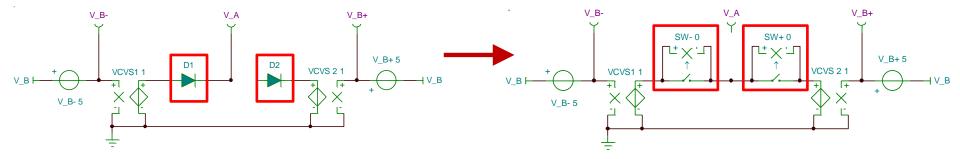

#### **SPICE tips – simplified components**

- Replace complex components with simple approximations if exact component modeling isn't necessary

- **Example:** ideal diode  $\rightarrow$  voltage-controlled switch

**Diode equation**:  $i_D = I_S(e^{\frac{qV_D}{kT}} - 1)$

SLYP725

#### ©2020 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated